GitHub repository

A repository of developed tools available to the scientific community is here.VERI-Place Algorithm

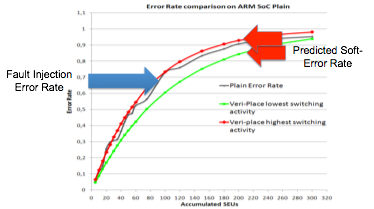

Software for accurate Soft-Error effects analysis and mitigation on Xilinx SRAM-based FPGAs. The tool performs the Soft-Error Analysis and the Placement of circuits on SRAM-based FPGAs oriented to the Soft-Error mitigation. A free DEMO executable version of VERI-Place tuned for the Xilinx Virtex-5 Genesys board (XCV5-VLX50T) is available for download. Download version v.6.0 - 12.06.2014

Software for accurate Soft-Error effects analysis and mitigation on Xilinx SRAM-based FPGAs. The tool performs the Soft-Error Analysis and the Placement of circuits on SRAM-based FPGAs oriented to the Soft-Error mitigation. A free DEMO executable version of VERI-Place tuned for the Xilinx Virtex-5 Genesys board (XCV5-VLX50T) is available for download. Download version v.6.0 - 12.06.2014

The software last release ( algorithm v.8.0 ) is available for various FPGAs upon user request and agreement. The following devices are nowadays available:

- Virtex5 xc5vlx50t-ff1136-2 release date 10.05.2014

- Virtex5 xc5vfx130t-1FF1738 release date 13.09.2015

- Zynq xc7z020-CLG484 release date 05.07.2015

- Kintex7 xc7k325t-2FF900C release date 14.09.2015

If you are interested in other devices please contact me by mail.

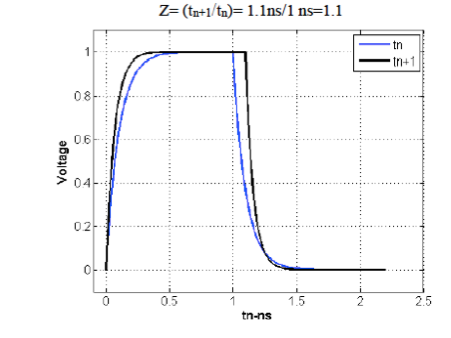

SETA algorithm

The Single Event Transient Analyzer (SETA) is a software for the analysis and mitigation of SET effects on ASIC and Flash-based FPGAs. The software is compatible with Microsemi Flash-based FPGAs. A version compatible with ProASIC A3P family is available for download upon user request and agreement.

The Single Event Transient Analyzer (SETA) is a software for the analysis and mitigation of SET effects on ASIC and Flash-based FPGAs. The software is compatible with Microsemi Flash-based FPGAs. A version compatible with ProASIC A3P family is available for download upon user request and agreement.

PDT FPGA model

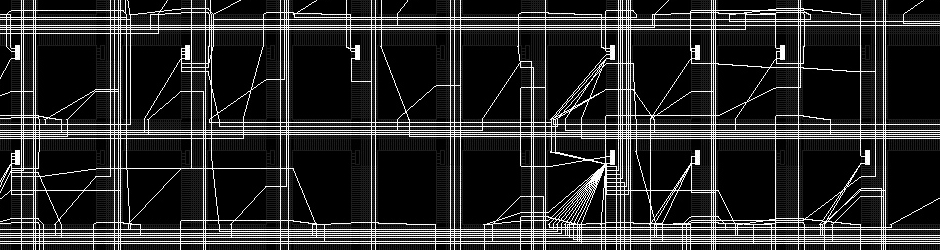

The (Politecnico Di Torino) PDT FPGA model is a fully parametric FPGA model that can be tuned on the basis of the logic and routing resources requirement. Look-Up Tables (LUTs), Flip-Flops (FFs), internal RAM, DSP cores and routing resources can be defined by the user. A complete tool chain is available (PDD Placement and Routing).

The (Politecnico Di Torino) PDT FPGA model is a fully parametric FPGA model that can be tuned on the basis of the logic and routing resources requirement. Look-Up Tables (LUTs), Flip-Flops (FFs), internal RAM, DSP cores and routing resources can be defined by the user. A complete tool chain is available (PDD Placement and Routing).

An image example of a placed and routed design is available here

A Synopsys Synplify compatible version is available for download upon user request and agreement.

GDS-II VLSI compatible Router Algorithm

It is an ASIC oriented routing tool compatible with the GDS-II VLSI standard. The tool is usable for radiation-sensitivity analysis, simulations, performances analysis and improvements.

It is an ASIC oriented routing tool compatible with the GDS-II VLSI standard. The tool is usable for radiation-sensitivity analysis, simulations, performances analysis and improvements.

An image example of an ASIC routed design is available here

A Synopsys Synplify compatible version is available for download upon user request and agreement.

HPC-driven Placement Algorithm

It is a GPGPU oriented placement tool compatible with the IBM layout standard. The tool has been successfully used to implement the IBM Superblue16 and Superblue 19.

It is a GPGPU oriented placement tool compatible with the IBM layout standard. The tool has been successfully used to implement the IBM Superblue16 and Superblue 19.

A Cadence compatible version is available for download upon user request and agreement.